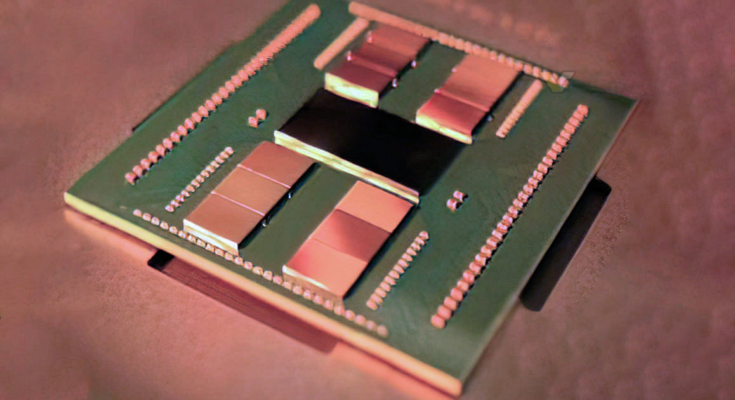

AMD Epyc Genoa with 12 chiplets pictured

Just yesterday the first photo of the new SP5 (LGA6096) socket has emerged and now we finally get to see the next-gen EPYC processor without the integrated heatspreader.

A Chiphell forum member “zhangzhonghao” appears to be the first person to reveal the real picture of the upcoming Zen4 server processor, codenamed Genoa. It is the first photograph showing all 12 chiplets installed on the SP5 package.

AMD EPYC “Genoa” CPU, Source: Chiphell

EPYC Genoa feature up to 96 cores and 192 threads in its full configuration. AMD will release many SKUs with partially disabled cores, so just because this processor has 12 chiplets it does not mean it will have all 96 cores active.

Each Zen4 CCD die has an area of 72 mm², which is 8 mm² smaller than Zen3 (such as on EPYC “Milan” series). The I/O die is smaller as well, around 397 mm² compared to 416 mm² on Zen3 EPYC CPUs. That said, AMD had no trouble fitting 6 chiplets on each side of the I/O die, considering that the SP5 (LGA 6096) package is also 37% bigger than SP3.

AMD 16-core EPYC Genoa processor, Source: VideoCardz

AMD’s new SP5 platform will support up to 12-channel DDR5 memory as well PCIe Gen5 interface. AMD Genoa is already shipping to first customers, according to AMD. The new EPYC 7004 series are now on track to launch by the end of this year.

| RUMORED AMD EPYC Processor Series Specifications | ||||||

|---|---|---|---|---|---|---|

| VideoCardz | 7001 “Naples” | 7002 “Rome” | 7003 “Milan” 7003 “Milan-X” (*) | 7004 “Genoa” | 7004 “Bergamo” | 7005 “Turin” |

| Launch | 2017 | 2019 | 2021 | 2022 | 2022 | 2023/2024 |

| Architecture | 14nm Zen | 7nm Zen2 | 7nm Zen3 | 5nm Zen4 | 5nm Zen4c | Zen5 |

| Socket | SP3 (LGA4094) | SP3 (LGA4094) | SP3 (LGA4094) | SP5 (LGA-6096) | SP5 (LGA-6096) | SP5 (LGA-6096) |

| Modules/Chiplets | 4xCCD | 8xCCD + 1xIOD | 8xCCD + 1xIOD | 12xCCD + 1xIOD | 12xCCD + 1xIOD | TBC |

| Max Cores | ||||||

| Max Clock | TBC | TBC | TBC | |||

| L2 Cache Per Core | 0.5 MB | 0.5 MB | 0.5 MB | 1 MB | TBC | TBC |

| L3 Cache Per CCX | 8 MB | 8 MB | 32 MB / 96 MB (*) | 32 MB | TBC | TBC |

| Memory Channels | ||||||

| Memory Support | ||||||

| PCIe Lanes | TBC | TBC | ||||

| Max cTDP | TBC | |||||

Source: zhangzhonghao @ Chiphell via @9550pro