Its an unusual disclosure, to say the least, as we d otherwise anticipate the compute pass away to be made on a single process. But with no more commentary from Intel offered, make from that what you will. Maybe theyre being uncomplicated, and they will in fact use 2 very different process nodes for the compute die?

The big revelation here is that we finally have some more concrete insight into what production processes the numerous tiles will use. The base tile of the GPU will be on Intels brand-new 10nm SuperFin process, and the Rambo Cache will be a generation newer still, using Intels future 10nm Enhanced SuperFin process. Its now confirmed that the Xe Link I/O tile, which will be utilized as part of Intels material to link together several Xe-HPC GPUs, will be built by an external fab.

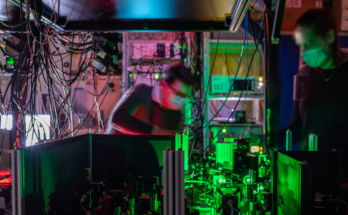

Continuing todays GPU news from Intels Architecture Day presentation, on top of the Xe-LP architecture instruction and Xe-HPG reveal, the business has likewise offered a quick roadmap update for their flagship sever-level part, Xe-HPC.

Better known by its codename of Ponte Vecchio, much to do has actually been made about Xe-HPC. The most complex of the Xe parts prepared, it is likewise the foundation of the Intel-powered Aurora supercomputer. Xe-HPC is pulling out all of the stops for performance, and to arrive Intel is employing every technique in the book, including their new-generation advanced product packaging innovations.

That leaves the matter of the calculate tile, the most performance-critical of the GPUs parts. With Intels 7nm procedure delayed by at least six months, the business has previously disclosed that they were going to take a “practical” approach and possibly use third-party fabs. And since their Architecture Day update, they still seem to be uncertain about– or a minimum of reluctant to reveal– just what they plan on doing. Instead, the calculate die is identified as “Intel Next Gen & & External”.