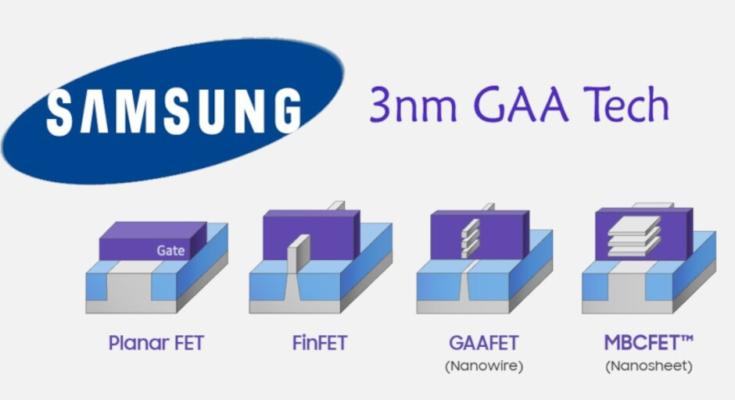

Samsung Foundry, the second-largest independent foundry worldwide after TSMC, has made some changes to its 3nm process node according to AnandTech. The first chips from Samsung Foundry to be produced using the 3nm process, 3GAE (3nm Gate-All-Around Early), will reportedly be going through high-volume manufacturing a year later than usual. It also was removed from Samsung’s roadmap indicating that 3GAE might be produced for internal use only.

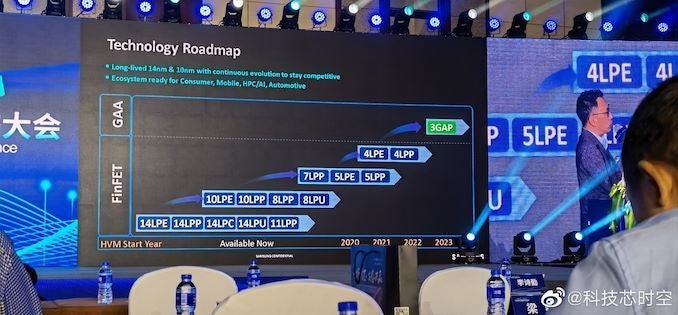

A Samsung representative said, “As for the 3GAE process, we’ve been in discussion with customers and expect to mass-produce 3GAE in 2022.” 3GAE’s successor, the 3GAP (3nm Gate-All-Around Plus) node still is listed on the roadmap with volume manufacturing expected to begin in 2023. The aforementioned roadmap was unveiled at Foundry Forum 2021 in China. Samsung Foundry introduced its updated tech roadmap which was then republished on Baidu and Weibo.

As for its chips using the older FinFET transistor architecture, Samsung has added 5LPP, and 4LPP to its roadmap with high-volume manufacturing set for 2021, and 2022, respectively. When Samsung unveiled its 3GAE and 3GAP nodes in May 2019, it announced that it would deliver a 35% increase in performance, a 50% reduction in power consumption compared to 7LPP which currently is the previous generation process node.

At the same time back in 2019, volume-production using 3GAA (Gate-All-Around transistor architecture) was announced to start in late 2021. With the new launch date of 2022 for the 3nm Gate-All-Around Early process, one can conclude that there has been a slight delay on Samsung’s part or a miscalculation. Either way, it is not considered a big deal as Sammy’s Early nodes aren’t used by manufacturers to a large degree.

Just a few days ago, Samsung Foundry taped out a 3nm chip that uses its Gate-All-Around (GAA) transistor architecture. Taping out a chip is the final act of its design cycle resulting in one of two outcomes: the chip design works or it doesn’t. In the case of the latter, a minor fix might be required or a complete overhaul of the design is called for.