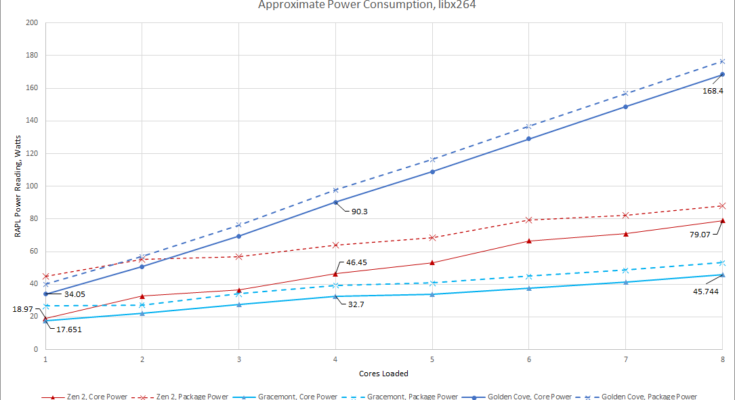

The winds of change are in the air for CPUs. Intel has long lorded over the computing world, and they remain a force to contend with, but many challengers gather at their gates. AMD, ARM, IBM, and other X86 designs sense a moment of weakness. In response, Intel released their Alder Lake platform with high-performance and high-efficiency cores, known as Golden Cove and Gracemont, respectively. [Clamchowder] and [cheese] have written up as many details as they were able to suss out about Gracemont.

ARM has done a multi-multi core design (big.LITTLE) for several years where they have a mix of high-power, high-performance cores and smaller, low-power cores. This allows the scheduler to make tradeoffs between power and performance. Typically the smaller cores in an ARM design are simpler in-order processors, having more in common with a microcontroller than with a full-scale desktop core. Many people have made an obvious comparison with the apparent similarities between ARM’s approach and Intel’s new offerings as Gracemont is based on Intel’s old Atom core, a low-power single issue, in-order processor.

[Clamchowder] and [cheese] were able to demonstrate that the Gracemont core in Alder Lake is nothing like Atoms of old or the tiny processors in ARM’s big.LITTLE. It is a multi-fetch, multi-issue, out-of-order processor. Given that it is so similar to the much more powerful Golden Cove processor, it gives us the chance to look into Intel’s tradeoffs to make a higher efficiency core. All of this information comes from significant guesswork and testing, slowly zeroing in on the sizes of different caches and the architecture of the branch prediction system.

It’s a fascinating read on the interworkings of a chip with real attention to detail. But, if you’re interested in peering even deeper, we covered extracting an actual gate from a processor.

Thanks [Carson Bunker] for sending this one in!